این مقاله بخشی از سری ارتباطات و طراحی سیستم است: Have SmartNIC – Will Compute

آنچه خواهید آموخت:

- توسعه یک زبان برنامه نویسی برای صفحه داده.

- اهمیت ترکیب برای قابل حمل NIC.

- مدیریت برنامه ها و داده ها با صفحه كنترل.

این پنجمین فصل از سری SmartNIC ما است ، و در اینجا ما راهی را كه SmartNICs و DPU می توانند طی كنند نشان خواهیم داد. ما مجموعه را با عنوان "چه چیزی SmartNIC هوشمند می کند؟" که در آن ویژگی هایی را که یک SmartNIC را از یک NIC معمولی جدا می کند ، تعریف کردیم. اساساً ، SmartNIC ها باید قابل برنامه ریزی باشند و کیت توسعه نرم افزار در دسترس مشتریان قرار گیرد. همچنین ، SmartNIC ها باید قدرت محاسباتی داخلی بسیار گسترده ای داشته باشند ، بسیار فراتر از یک NIC استاندارد ، موجود برای برنامه نویسی.

ما سپس به سراغ "چرا SmartNIC بهتر از NIC معمولی هستیم؟" در اینجا ، ما سعی کردیم عناصر محاسباتی را به NIC اضافه کنیم که آن را هوشمند می کند. همچنین در مورد انواع برنامه هایی که می توان از طریق SmartNIC اجرا کرد ، همراه با مزایای بارگیری CPU میزبان از این پردازش اضافی ، بحث شد.

در سومین بخش خود ، "SmartNIC Architectures: یک تغییر به شتاب دهنده ها و چرا FPGA ها آماده تسلط هستند" ، ما همه محصولات برتر SmartNIC در بازار و هر یک از معماری های آنها را بررسی کردیم. ما همچنین بررسی کردیم که چرا FPGA در نهایت در این بازار تسلط پیدا می کند – اشاره می کند این خط لوله است که به سخت افزار تسریع شده است.

آخرین ورودی در این مجموعه "How PCIe5 with CXL، CCIX، and SmartNICs Change Solutions Acceleration" بود که به تغییراتی که در PCIe ایجاد می شد با افزودن پروتکل های جدید طراحی شده برای ارتباط بیشتر SmartNIC ها و شتاب دهنده ها اشاره داشت. در این مقاله ، ما یک آینده احتمالی برای SmartNIC ها را مرور خواهیم کرد – آینده ای که معماری آن قابلیت حمل دارد. قابلیت حمل و نقل نیز قابلیت برنامه نویسی و قابلیت انعطاف پذیری دارد که ما را به سمت یک پلت فرم نرم افزاری تعریف شده و سخت افزاری سوق می دهد. ابزارهای موجود برای مشتریان برای برنامه ریزی آنها. یک قسمت اساسی از این مشکل فقدان واقعی یک زبان برنامه نویسی در سطح صنعت برای اجزای شبکه بوده است.

همزمان با تکامل دستگاه های شبکه مانند روترها ، سوئیچ ها و NIC ها ، آنها صفحه داده را از صفحه کنترل جدا کردند. صفحه داده داده های منحصر به فرد داده را پردازش می کند ، بسته ها نامیده می شوند و به سرعت آنها را از طریق دستگاه جابجا می کند. بسته هایی با اطلاعات مسیریابی یکسان جریان را تشکیل می دهند. طی چند دهه گذشته ، صنعت نوآوری های زیادی در مورد چگونگی مدیریت موثرتر جریان ها از طریق صفحه داده ارائه داده است.

در سال 2014 استانداردي ارائه شد كه بر اين نوآوري ها متمركز بود و كنسرسيوم زبان P4 راه اندازي شد. P4 یک زبان منحصر به فرد خاص برای دامنه است که حول مفهوم برنامه نویسی صفحه داده ساخته شده است.

به عنوان یک زبان ، P4 به گونه ای طراحی شد که مستقل از اجرا باشد ، به این معنی که برنامه های نوشته شده در P4 به راحتی برای هر تعداد سیستم عامل هدف P4 دوباره کامپایل می شوند ، و سپس آنها باید بر روی این سیستم عامل ها کار کنند. این قابلیت جابجایی کد را در سازمانی که چندین سیستم عامل هدف P4 ممکن است وجود داشته باشد امکان پذیر می کند ، هرکدام با سخت افزارهای مختلف پردازش سخت افزاری متفاوت هستند.

بنابراین ، یک مهندس می تواند یک برنامه P4 بنویسد که یک روند امنیتی خاص شرکت را اجرا می کند ، سپس این برنامه را روی همه روترهای شرکت ، سوئیچ ها و در نهایت SmartNIC های P4 نصب کنید. این محصولات حتی می توانند از فروشندگان مختلف باشند. همه آنها باید سیستم عامل های هدف P4 معتبر باشند. P4 قابلیت حمل کد را فراهم می کند ، که برای سیستم های بسیار پیچیده هماهنگ شده در ارائه دهندگان خدمات ابری (CSP) و مراکز داده فوق مقیاس بسیار حیاتی است.

ترکیب پذیری

جنبه مهم بعدی قابل حمل NIC قابلیت ترکیب است. این قابلیت گرفتن ماژول های مختلف است که بیشتر آنها با P4 نوشته شده اند و مونتاژ آنها در یک ساختار منسجم صفحه داده با قرار دادن ماژول ها در داربست ارائه شده توسط یک ساختار انعطاف پذیر و قابل حمل SmartNIC.

این معماری اغلب دارای رابط هایی با دو عنصر تعریف شده سخت افزاری است ، موتورهای دسترسی مستقیم حافظه (DMA) و کنترل دسترسی رسانه (MAC). موتور DMA از طریق گذرگاه PCIe با CPU میزبان ارتباط برقرار می کند. این اغلب از نظر معماری خاص از نظر سخت افزاری است که از مدارهای خاص هندسه آن تراشه بهره می برد. به همین ترتیب ، موتور MAC از مدارهای ارتباطی مشابهی برای ارتباط با شبکه اترنت نیز استفاده می کند.

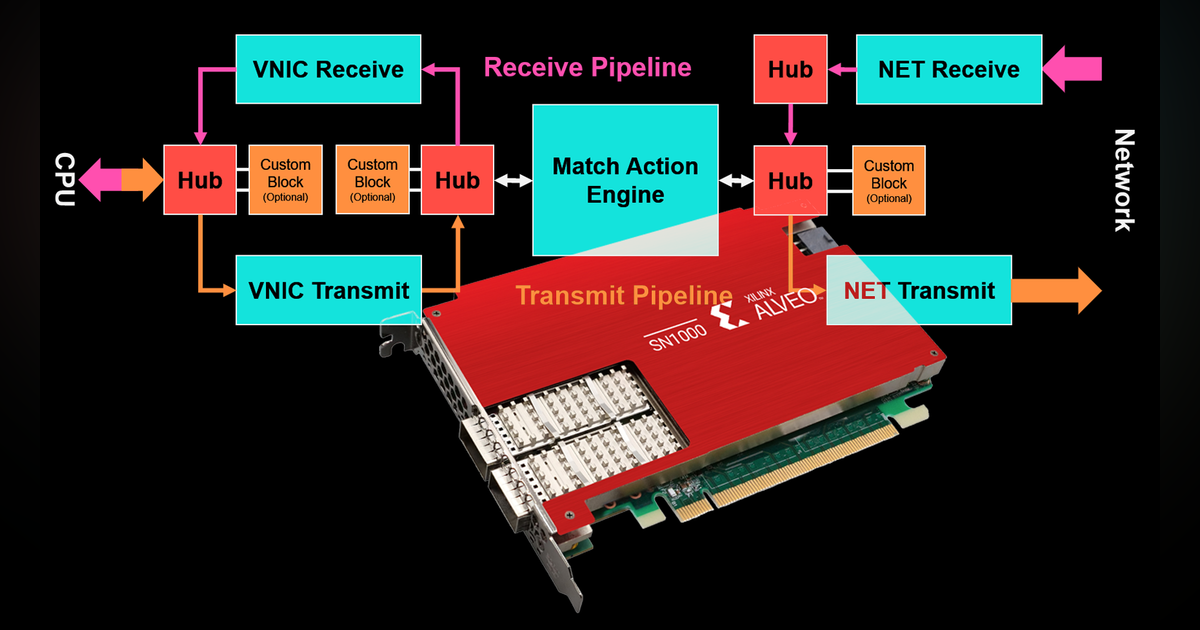

به همین ترتیب ، هر دو بلوک خط لوله هواپیمای داده بلوک های منطقی سختی هستند که روی تراشه راننده SmartNIC وجود دارد. تمام بلوک های معماری NIC قابل ترکیب بیشتر به صورت ماژول های P4 نوشته می شوند. این چهار نوع بلوک اصلی ، هاب هایی هستند که نقاط ورودی ماژول های پلاگین ، یک NIC مجازی (vNIC) ، موتور مطابقت (MAE) و موتورهای شبکه (NET) هستند. NIC قابل ترکیب است زیرا صفحه داده به راحتی بلوکهای منطقی اضافی را در نقاط مختلفی که ماژولها را می توان به برق متصل کرد می پذیرد (شکل 1) .

٪ {[ data-embed-type=”image” data-embed-id=”609c2996c0152f214b8b45e5″ data-embed-element=”span” data-embed-size=”640w” data-embed-alt=”1. The composable NIC streaming subsystem architecture data plane readily accepts additional logic blocks at various points where modules can be plugged in.” data-embed-src=”https://img.electronicdesign.com/files/base/ebm/electronicdesign/image/2021/05/ED5_Figure1v3.609c2995d5df3.png?auto=format&fit=max&w=1440″ data-embed-caption=”1. The composable NIC streaming subsystem architecture data plane readily accepts additional logic blocks at various points where modules can be plugged in.” ]}٪

بلوک های سفارشی را می توان با P4 ، C / C ++ ، HLS و RTL نوشت و سپس مستقیماً در صفحه داده قرار داد. این بلوک های سفارشی با هاب هایی متصل می شوند که عملکردهای مالتی پلکس ، بافر و مسیریابی را بین پردازنده های جریان فراهم می کنند. این امر نهایت انعطاف پذیری را در مورد مدیریت جریان های شبکه برای مشتریان فراهم می کند.

بلوک های vNIC با P4 نوشته شده اند و یک رابط NIC سنتی برای درایورهای دستگاه سیستم عامل (OS) ارائه می دهند. یک یا چند vNIC می تواند وجود داشته باشد ، و می توان آنها را از طریق پورت به برنامه های خاص نگاشت کرد. این امر همچنین بای پس هسته را برای برنامه هایی که به دنبال بهترین عملکرد هستند ، می گذارد. MAE توابع Open vSwitch (OvS) را برای هسته های پشتیبانی کننده کانتینرها یا ناظران کنترل کننده چندین ماشین مجازی (VM) اداره می کند. همچنین می توان از MAE برای اجرای فیلترهای مناسب که فایروال بالقوه سیستم را در SmartNIC ایجاد می کنند ، استفاده کرد.

سرانجام ، ما NET بلوک های دریافت و انتقال را داریم که عملکردهای بسته اصلی ورودی و خروج ، ویژگی های معمولی NIC و تخلیه های بدون حالت را مدیریت می کند. همانطور که در شکل 1 نشان داده شده است ، ورودی های مناسب در داربست قابلیت حمل قابل حمل SmartNIC را تشکیل می دهند تا مشتریان بتوانند در هر کجا که صلاح می دانند کد را در هر دو خط لوله صفحه داده دریافت و انتقال وارد کنند.

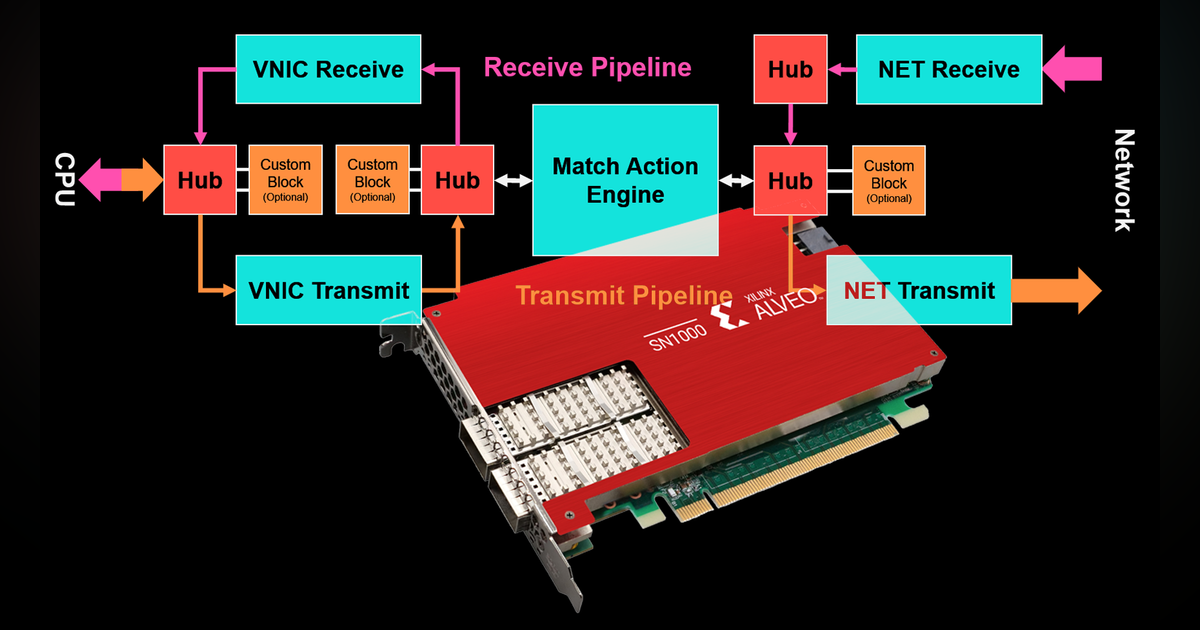

تمام ماژول های قابل ترکیب در خطوط لوله صفحه داده با رنگ قرمز نشان داده شده در شکل 1 با منطق قابل برنامه ریزی اجرا می شوند. این بدان معناست که رفع اشکال ها و اضافه شدن ویژگی های آینده مسئله ساده بروزرسانی بیت هایی است که NIC قابل حمل را تشکیل می دهند. NIC های سنتی تقریباً منطقی کاملاً سخت هستند – مطمئناً ، بعضی اوقات می توانید میان افزار جدیدی را در آنها بارگذاری کنید ، اما بسیاری از مواردی که NIC را به NIC تبدیل می کند ، از روزی که محصول ارسال می شود ، در سیلیکون تنظیم می شود. همانطور که در شکل مشاهده می کنید ، فقط سه نوع بلوک ثابت شده است. همه موارد دیگر روان هستند و می توانند به روز شوند. این به این معنی است که NIC قابل حمل از نظر نرم افزاری تعریف شده و از نظر سخت افزاری تسریع می شود. عملکرد صفحه داده بسیار مهم است زیرا با افزایش سرعت اترنت ، سرعت بسته داده نیز افزایش می یابد. در شکل 2 ، صفحه داده را برای معماری SmartNIC مبتنی بر هسته Arm نشان می دهیم. صفحه داده در یک رویکرد Arm Arm با عبور داده های بسته به جلو و عقب بین هسته های بازو و بلوک های منطقی ، متراکم می شود.

٪ {[ data-embed-type=”image” data-embed-id=”609c29ae66c903a6198b47c5″ data-embed-element=”span” data-embed-size=”640w” data-embed-alt=”2. The data plane in an Arm core approach will become congested as it passes packet data back and forth between memory.” data-embed-src=”https://img.electronicdesign.com/files/base/ebm/electronicdesign/image/2021/05/ED5_Figure2.609c29add0fca.png?auto=format&fit=max&w=1440″ data-embed-caption=”2. The data plane in an Arm core approach will become congested as it passes packet data back and forth between memory.” ]}٪

در این مثال ، هسته Arm در مرحله 1. پردازش بسته ای را انجام داده است. سپس در مرحله 2 ، آن بسته را به حافظه DRAM هل می دهد. در مرحله 3 ، یک "شتاب دهنده" آن بسته را از DRAM وارد می کند تا عملیاتی انجام دهد. در مرحله 4 ، پس از کار با بسته ، شتاب دهنده بسته را مستقیماً در حافظه پنهان هسته Arm دیگر کپی می کند. در مرحله 5 ، هسته Arm پس از کار بر روی بسته ، سپس آن را مجدداً در DRAM کپی می کنید. سرانجام ، در مرحله 6 ، شتاب دهنده آن بسته را از DRAM می کشد و از طریق موتور DMA به CPU میزبان هل می دهد.

با افزایش نرخ بسته به این SmartNIC مبتنی بر بازو ، به ویژه به صدها میلیون بسته در ثانیه ، میزان تولید کلی NIC آسیب می بیند ، بسته ها رها می شوند و انتقال مجدد آغاز می شود ، که باعث تشدید بیشتر مسئله. بسته ها بطور مداوم به اطراف منتقل می شوند ، اغلب از طریق حافظه باعث ایجاد ازدحام در گذرگاه DRAM می شود.

شکل 1 نشان می دهد که معماری منطقی قابل برنامه ریزی از طریق خط لوله انجام می شود ، به این معنی که می تواند مقدار زیادی بسته را بخورد. بسته ها از طریق مراحل خط لوله عبور می کنند ، همه به طور موازی کار می کنند و نیازی به انتقال بسته ها از حافظه DDR نیستند. این عملیات به دلیل محاسبات منطق دروازه و نه دستورالعمل های کلاسیک واکشی و اجرای پردازنده ، روی بسته ها اتفاق می افتد. این بدان معنی است که با هر تیک ساعت ، تمام مراحل موازی هر خط لوله در حال انجام عملیات منطقی بر روی بسته ها هستند. این همان معنای شتاب سخت افزاری است.

مدیریت از طریق Control Plane

ما هنوز هواپیمای کنترل را لمس نکرده ایم. این اغلب مجموعه ای از هسته های بازو است که برنامه ها و داده های وارد شده در بلوک های منطقی و جداول جستجوی مورد استفاده توسط صفحه داده را مدیریت می کند. صفحه کنترل همچنین اطلاعات آماری مفید برای مدیریت بیشتر و اندازه گیری عملکرد عناصر اصلی را در NIC جمع آوری می کند. وظایف صفحه کنترل به موازات صفحه داده اتفاق می افتد و نباید عملکرد کلی NIC را پوشش دهد.

صفحه کنترل امکان مدیریت سطح نرم افزار صفحه داده را فراهم می کند ، اجازه می دهد عنصر تعریف شده توسط نرم افزار در یک معماری NIC قابل حمل باشد. قسمت دیگر صفحه کنترل ، کنترل استثناست. هنگامی که یک بسته جدید وارد می شود ، که یک قاعده جریان برای آن وجود ندارد ، یک رویداد استثنا رخ می دهد ، که توسط صفحه کنترل اداره می شود. این استثنا همچنین می تواند به CPU میزبان ارسال شود تا تصمیم بگیرد آیا بسته معتبری است. اگر بسته معتبر باشد ، می توان یک قاعده جریان را توسط هسته کنترل بازو یا CPU میزبان به MAE اضافه کرد. سپس تمام بسته های بعدی به طور کامل در صفحه داده اداره می شوند.

علاوه بر تمام توابع صفحه داده که در بالا بحث شد ، برنامه های محاسباتی شدید مانند IPSec ، kTLS و DPI / Regex ، که ممکن است مقادیر قابل توجهی از چرخه های CPU میزبان را مصرف کنند ، می توانند با هسته های بازو اجرا شوند. در صفحه کنترل این امکان بارگیری مجدد این برنامه ها را مستقیماً در SmartNIC فراهم می کند ، جایی که می توان آنها را با استفاده از معماری پلاگین پیاده سازی کرد.

نمودار نقشه راه

ابرمقیاسان ، CSP ها و مشتریان بزرگ مرکز داده ، آنها خواهان دیدن نقشه راه محصول فروشنده SmartNIC خواهند شد. در فناوری ، نقشه راه ها یک جدول زمانی را ترسیم می کنند ، که معمولاً 18 تا 36 ماه طول می کشد و این تعهد فروشنده به یک خط تولید مشخص را به مشتریان نشان می دهد.

در سال 2007 ، اینتل مدل تولید Tick-Tock را معرفی کرد ، به این معنی که یک چرخه ، تیک ، یک پلت فرم بهبود یافته است و چرخه بعدی ، تغییر هندسه تراشه است. در حالی که همه مانند اینتل نیستند ، اما صنعت اغلب سرعت آنها را منعکس می کند. برای SmartNICs ، این اغلب سیلیکون جدیدی است و تغییرات نرم افزاری یا برد روی صفحه را دارد. زمان بین کنه ها به طور معمول دو سال بود. این بازده کافی در تراشه را تضمین می کند. در واقع ، یک معماری قابل حمل SmartNIC سیستم عامل NIC است.

با تغییر ساختار توسعه NIC کلاسیک به عنوان یک پروژه نرم افزاری ، به جای پروژه طراحی مدار مجتمع (ASIC) مخصوص برنامه ، این تیم NIC را آزاد می کند تا با توجه به نیازهای کسب و کار ، با سرعت بیشتری پیشرفت کند. همچنین ، توسعه تراشه می تواند بر پیشرفت در منطق ورودی / خروجی PCIe و Ethernet و نوآوری در منطق قابل برنامه ریزی و صفحه کنترل باشد. توسعه هیئت مدیره بیشتر به مسئله پشتیبانی از تراشه جدید و گرما و قدرت آن تبدیل می شود ، نه در مورد انطباق با لیست فزاینده ویژگی ها و تخلیه های درخواست شده توسط بازاریابی. داشتن یک NIC قابل حمل واقعی امکان پیشرفت نرم افزاری و سخت افزاری را به صورت موازی و نه قدم قدم فراهم می کند.

این برای نقشه راه به چه معناست؟ ساده ، این به مشتریان نشان می دهد که یک سیستم عامل NIC سازگار وجود دارد که تکامل می یابد ، در طول مسیر ، ویژگی های جدید در سیستم عامل ظاهر می شود. علاوه بر این ، ماژول های پلاگین اضافی توسط فروشنده و اشخاص ثالث در دسترس قرار می گیرد تا دامنه برنامه های موجود در NIC را افزایش دهند. این تیم های توسعه تراشه و برد را آزاد می کند تا به صورت موازی با تیم قابل حمل NIC اجرا شوند. هر محصول روی نقشه راه برای هر سه گروه نقطه همگرایی خواهد بود.

فناوری همیشه به سمت جلو حرکت می کند. امروز ما در مورد SmartNIC های قابل برنامه ریزی ، قابل ترکیب و قابل حمل P4 صحبت می کنیم که با منطق قابل برنامه ریزی نصب می شوند و مجموعه ای بسیار کارآمد از خطوط لوله پردازش بسته های سریع را ایجاد می کنند. اخیراً ، Xilinx در انتشار Alveo SN1000 SmartNIC جدید خود ، رویکرد فوق را در پیش گرفت.

در آینده ، ساخته های جدید قابل حمل SmartNIC روی تراشه های پیشرفته تری نیز اجرا می شوند. این تراشه ها از هزاران موتور یادگیری ماشین ، یک شبکه با عملکرد بالا روی تراشه (NoC) و موتورهای DMA قابل ترکیب استفاده می کنند. آینده درخشان است و دیدن اینکه چگونه فناوری تعریف شده توسط نرم افزار و شتاب سخت افزاری با گذشت زمان تکامل می یابد ، هیجان انگیز خواهد بود.